# It's time to rethink...

## ...advanced process dummy fill

XYALIS increases the productivity, reliability, and capability of dummy fill with GOTstyle, a leading-edge fill engine that handles the largest designs with maximum performance and minimum memory requirements thanks to the new GDSII & OASIS® (GOT) engine.

Dummy tiles must be inserted in low-density design areas, to help flatten the surface of each metal layer before CMP. These additional polygons, though electrically inactive, may cause parasitic effects that must be minimized and taken into account early in the design process to avoid behavioral and timing issues. Dummy fill is mandatory for process but providing a way to fine tune it is a must for designers.

- Patented advanced insertion algorithm

- · Optimal result file size

- Parasitic effect minimization

- Support for advanced nodes, 10nm and below

- Complex dummy tiles instantiation

- Tile interconnection

- Multi-pass insertion for complex fill operations and high performance parallelization

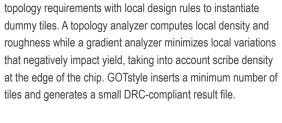

GOTstyle redesigned fill engine optimizes new fill methodologies required for the most advanced processes, including dual- and quad-patterning. GOTstyle maximizes CMP yield with a highly accurate patented tile insertion algorithm based on local density and roughness calculations and their variations over large areas.

GOTstyle minimizes parasitic effects by limiting the number of dummy structures and positioning them away from active geometries. Balancing dummy tile insertion around critical nets allows for precise control of impact on timing.

GOTstyle

#### ESSENTIAL COMPANION TOOLBOX

XYALIS offers a set of tools dedicated to layout manipulation that can process the largest GDSII and OASIS® database, with the highest processing speed and lowest memory requirement, and provide a safe transfer to silicon for the most complex SOC designs.

#### SYSTEM REQUIREMENTS

Runs on any Linux workstation with RedHat 6 or above. Management of multi-core is automatic. A Mac OSX version is also available.

Binaries for other platforms may be provided on request.

#### INFORMATION

For more information on products or services please visit www.xyalis.com or e-mail sales@xyalis.com

### **Features and Benefits**

#### Support for advanced nodes, 10nm and below

GOTstyle grid-based insertion combined with adjustable alignment grids and automatic cuts of dummy lines enables horizontal and vertical alignment of dummies and slots for simpler mask manufacturing in case of dual- and quadpatterning.

#### Complex dummy tiles instantiation

GOTstyle inserts any type of dummy tiles, whatever their complexity: full-layers, regular tiles, post-OPC cells, diodes for grounding to bulk. To better control density over the different areas of the design, the insertion algorithm computes the optimum tile size and merges dummy tiles into larger blocks if necessary.

#### Tile interconnection

GOTstyle offers the possibility to replace floating capacitance of disconnected dummy tiles with efficient shielding by inserting interconnection cells between contiguous dummy tiles. Interconnection cells may be defined horizontally and vertically, making it possible to stack dummy tiles through layers and to build dummy stripes within a layer.

#### Multi-pass insertion for complex fill operations and high performance

By staging dependencies between different layer fill operations GOTstyle handles complex dummy fill generation with reduced computing and memory footprints. Staged insertion is also used to distribute multi-layer fill across many cores in order to dramatically speed up calculation.

Advanced insertion algorithm with optimal result file size GOTstyle patented insertion algorithm combines global

#### • Parasitic effect minimization

Advanced features such as the patented Keep Away function that increases space between inserted dummy tiles and critical nets and non orthogonal insertion grid for better net balancing minimize parasitics generated by dummy fill and avoid parasitics variations along the design grid.

#### **European Headquarter**

World Trade Center BP 1510 38025 Grenoble cedex 01 France

#### **XYALIS USA**

14938 Camden Avenue Suite 216 San Jose, CA 95124 USA

#### **XYALIS Asia**

541 Orchard Road #09-01 Liat Towers Singapore 238881 Singapore