XYALIS at DAC Conference 2025: #booth 2628

News & Press

XYALIS at DAC Conference 2025: #booth 2628

3D-ICs, stitching, MPWs, PCMs, multi-patterning, or density management create disruptions, bottlenecks, and inefficiencies in your existing Mask Data Preparation flow?

Visit XYALIS @DAC to learn how XYALIS transforms Mask Data

Preparation with end-to end automation from specs to masks, and reduces engineering

time by up to 40-70% while improving quality and cutting silicon usage by 10-15%.

Legacy MDP workflows often struggle to keep up with the increasing intricacy of specifications and constraints, creating bottlenecks, increasing engineering time, and elevating risks of costly errors or silicon waste. In this context, the need for a fully automated, intelligent, and flexible MDP solution is more critical than ever.

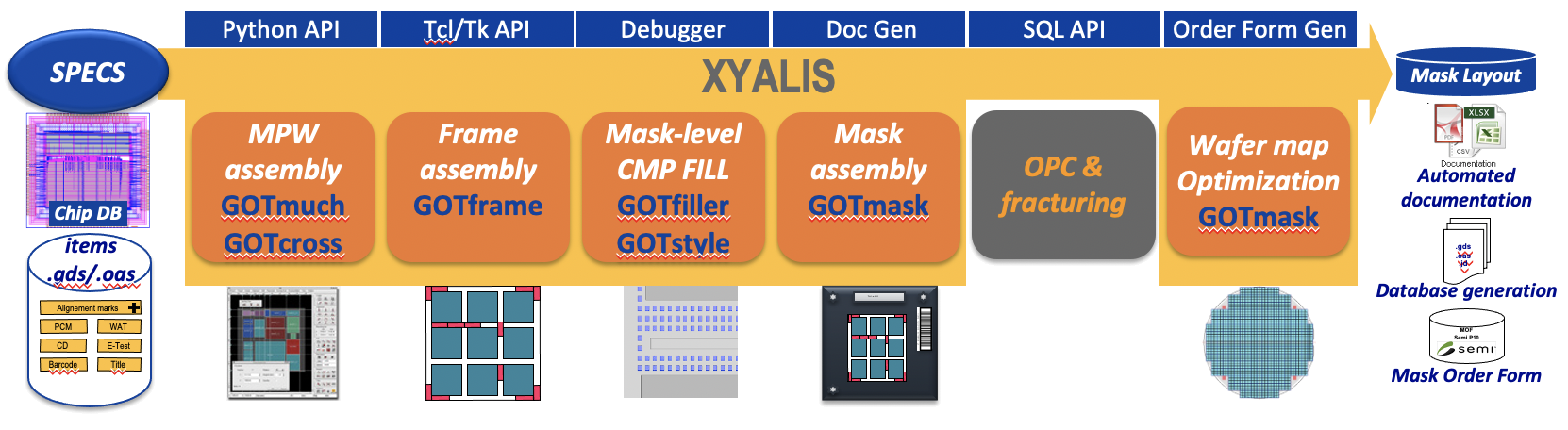

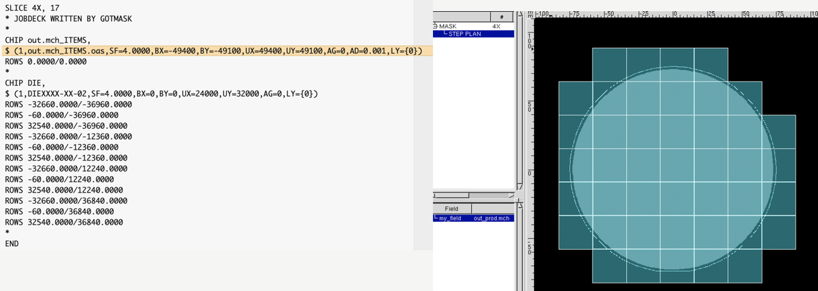

XYALIS addresses this challenge head-on by delivering a next-generation, end-to-end Mask Data Preparation platform. Our solution leverages specialized engines, deep domain expertise, and automation from design specifications to final mask data, drastically reducing manual intervention and engineering effort.

Key benefits:

- Up to 40–70% reduction in engineering time

- 10–15% reduction in silicon usage

- Improved data quality, consistency, and reliability

- Seamless integration with existing tools and flows

- Customizable modules to target specific pain points (e.g., MPW merging, stencil optimization, rule-based validation)

One of our customers put it best:

“XYALIS’ customizable solution addressed bottlenecks and inefficiencies in our existing MDP flow with their specialized engines and domain expertise.”

At DAC, we are proud to showcase how XYALIS is transforming MDP from a constraint into a competitive advantage — enabling chipmakers to move faster, optimize resources, and meet the demands of modern semiconductor design.

Focused on ease of use and computing and memory performance, based on production proven building blocks, XYALIS MDP tools will help you to improve your flow for a better yield.

Support for SEMI standards, powerful scripting capabilities, and now a communication link to any SQL database make XYALIS MDP tools easy to integrate in any customer design or manufacturing flow.

XYALIS will also demonstrate at the DAC 2025 conference GOTstyle and GOTfiller, CMP fill engines. These tools deliver unsurpassed computing and memory performance for the most advanced processes at the chip and reticle level.

Conference details

See us at DAC 2025 conference, San Francisco, Moscone West, June 23-25, on booth #2628.

- Monday, June 23 from 10:00 am to 6:00 pm

- Tuesday, June 24 from 10:00 am to 6:00 pm

- Wednesday, June 25 from 10:00 am to 6:00 pm